侧重点不同仿真即使用项目模型将特定于某一具体层次形式验证与仿真区别的不确定性转化为它们对目标的影响,该影响是在项目仿真项目整体的层次上表示的 形式化在逻辑科学中是指分析研究思维形式结构的方法形式化验证利用形式化方法,即基于严格的数学表述和模型,根据设计规约对设计功能进行属性描述,并自动进行数学。

仿真验证是根基和基础,无论是否精通形式验证和FPGA原型验证,只要仿真技术熟练,对求职市场而言优势显著形式验证虽可作为仿真技能的补充,对于解决仲裁类模块问题尤其方便,但它的应用范围有限,尤其是需要对RTL设计有深入理解,特别是在时序方面目前,其主要应用多局限于特殊模块,真正的挑战在于建模FPGA。

形式验证补充了模拟验证的不足,二者各有优势,互为补充,缺一不可仿真是一种基于经验的模拟验证方法,通过反复试验试图查明缺陷,这要花相当多的时间尝试所有可能的组合,因此永远不会完整另外,由于工程师必须定义和产生大量输进条件,形式验证与仿真区别他们的工作重点将是如何在非设计目标基础上分解设计形式验证是穷。

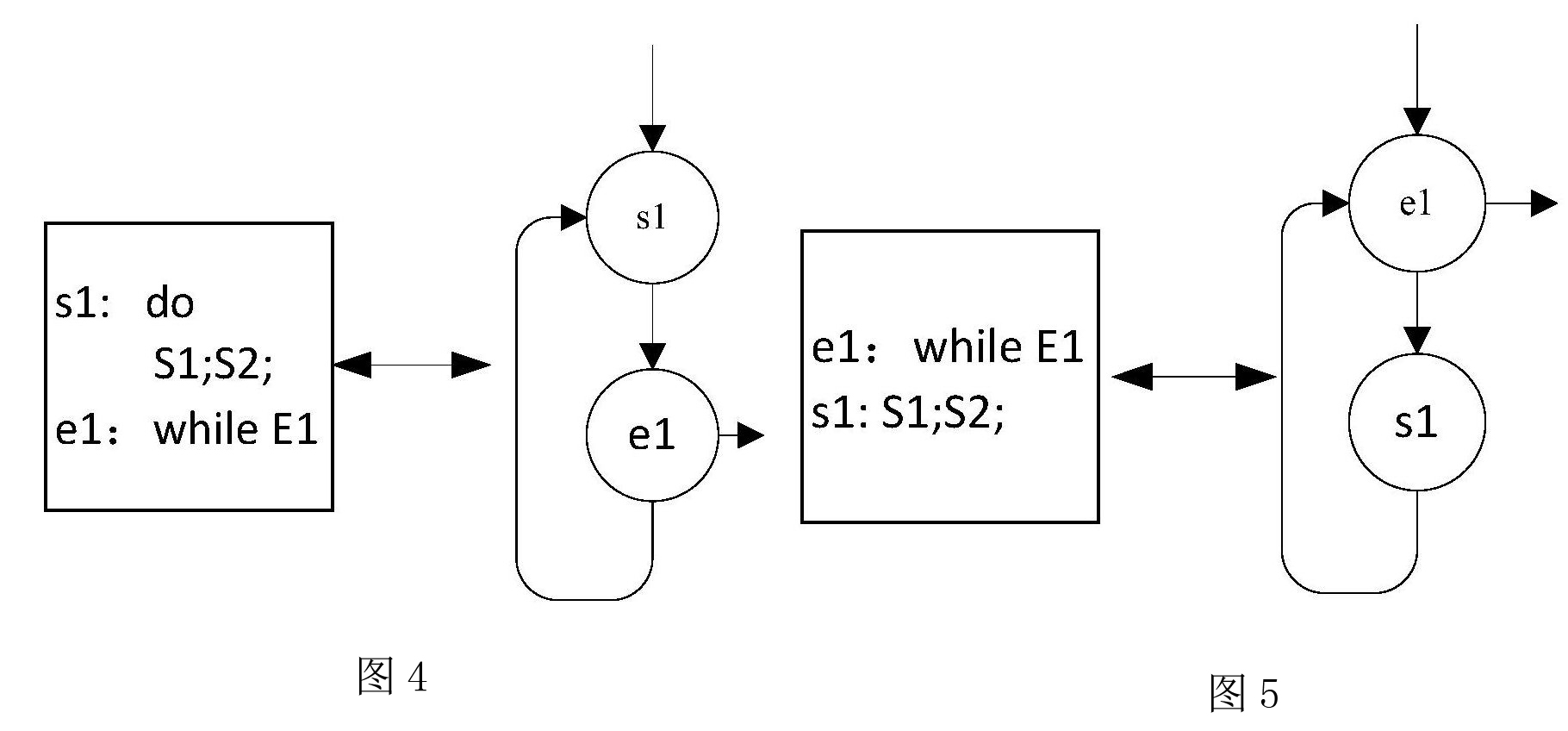

形式验证是一种高效精确的验证方法,用于证明设计的实现逻辑与参考设计的逻辑等价相比于逻辑仿真,形式验证无需构造测试激励,其速度快检查覆盖率高,但不检查时序错误在形式验证中,逻辑等价性检查是最成熟的方法实现设计与参考设计的逻辑锥由DFF为顶点的逻辑结构进行逐一比较,以确认两者逻辑。

它们在设计流程中的不同阶段发挥关键作用,帮助设计者确保设计的一致性与正确性模拟仿真与形式验证在验证过程中各有优势,技术互补形式验证通过数学证明确保设计的正确性,而模拟仿真则通过实际运行测试设计的性能结合使用这两种方法,可以更全面地找出设计中的所有问题,提高设计质量。

关于形式验证的普遍误解,本文揭示了其在芯片开发中的重要性,尽管曾经被视为外来技术形式验证通过数学证明确保设计的正确性,区别于仿真无法完全验证的bug然而,尽管被广泛使用,一些设计者和验证工程师仍对其抱有误解,导致应用普及受限以下是关于形式验证的11个常见误区的澄清并非只有博士能掌握。

模型检查主要是检查RTL代码是否满足规范中规定的一些特性在规定这些特性时一般使用特性规范语言,一般也使用基于断言的验证语言由于这种方法可以在不需要仿真的前提下检查设计中所有可能出现的情况是否满足规定的特性,所以使用这种方法不会遗漏任何的边界情况。

在芯片验证领域,模拟仿真验证和形式化验证两者相辅相成,各司其职前者更适合系统级别的功能验证,而后者更关注模块级别此外,FPGA的硬件加速测试也是重要一环,与上述方法形成互补形式化验证的核心可以理解为一套严格数学算法与模型驱动的过程,工程师的任务是将设计的功能转化为电路规则的描述,并。

SVA模块和工具的巧妙运用是formal验证的关键,property的设置有“assume”和“assert”两种策略例如,当测试模块A与B的输入输出关系时,推荐先添加assumption,避免一开始就过于严格忆芯STAR2000项目中的应用,展示了形式验证在解决复杂设计难题时的卓越效果,它能够揭示传统仿真难以触及的瑕疵公共SVAPSL。

形式化验证是数学方法在证明系统无错误的应用它通过构建精确的数学模型,定义系统在不同时间点应有的状态,以限制系统设计与实现此方法在硬件设计领域尤其流行,因硬件设计周期长,成本高,一旦生产完成,修改难度大而软件领域,形式化验证虽长期有研究,但常见度较低,主要是由于软件迭代快速,频繁更新。

然而,当形式验证与仿真区别我们将视线转向工业界和工程技术领域,quot数值仿真quot这个词就显得更为生动活泼它往往与数值方法计算分析等紧密相连,将理论知识与实践操作相结合,为设计优化和预测工程系统的行为提供关键支持例如,我们可能听到quot流体仿真quot或quot运动仿真quot这样的表述,它们强调的是实际应用中的模拟和验证,旨在。

仿真实验是一种利用计算机技术和数学模型来模拟真实实验过程和现象的方法仿真实验具有以下几个显著特点1 可重复性和灵活性仿真实验允许研究人员反复运行相同的实验条件,以验证结果的一致性和可靠性同时,仿真实验可以灵活地调整实验参数和条件,以探索不同情境下的实验结果这种灵活性使得研究人员。

相比于动态仿真,形式验证的优势主要体现在其验证的精确性和完整性尽管其缺点可能包括计算资源需求大和验证时间长等问题,但在复杂设计的验证中,其优势显著启动Gui界面,输入“fm”或“formality”Formality验证流程可以分为以下几个主要步骤1 **读入RTL设计文件**通过“read design file”命令。

你好,我研究生期间做的是这个方向,我说说我的了解,仅供参考~软件开发中一般使用“测试”来找bug,这种方法只能找到bug,不能证明程序没有bug形式化验证是用逻辑来验证程序的可靠性,就是把一段程序用逻辑的方法证明一遍,证明它能得到预期的结果,没有bug一般这类研究主要应用于昂贵的航天器材的。

完成RTL设计后,紧接着进行仿真和验证通过各种测试用例,确保RTL设计满足性能和功能需求这一步骤可能需要反复迭代,以确保设计的正确性随后,进行逻辑综合,将高级的RTL描述转换成门级网表,同时插入DFT设计可测试性功能,以支持后续的测试过程形式验证用于验证逻辑综合的结果是否符合设计要求物。

Formal Verify,即形式验证,核心理念是使用数学证明手段来确保修改后设计与原始设计在功能上的等价性此验证方法常用于比较设计的两个版本,如 RTL 级设计与门级网表综合后的门级网表与布局布线优化后的门级网表其中,Synopsys公司的Formality是常用的工具对DFT工程师而言,形式验证任务包括两项。

本文仅代表作者观点,不代表百度立场。

本文系作者授权百度百家发表,未经许可,不得转载。

发表评论